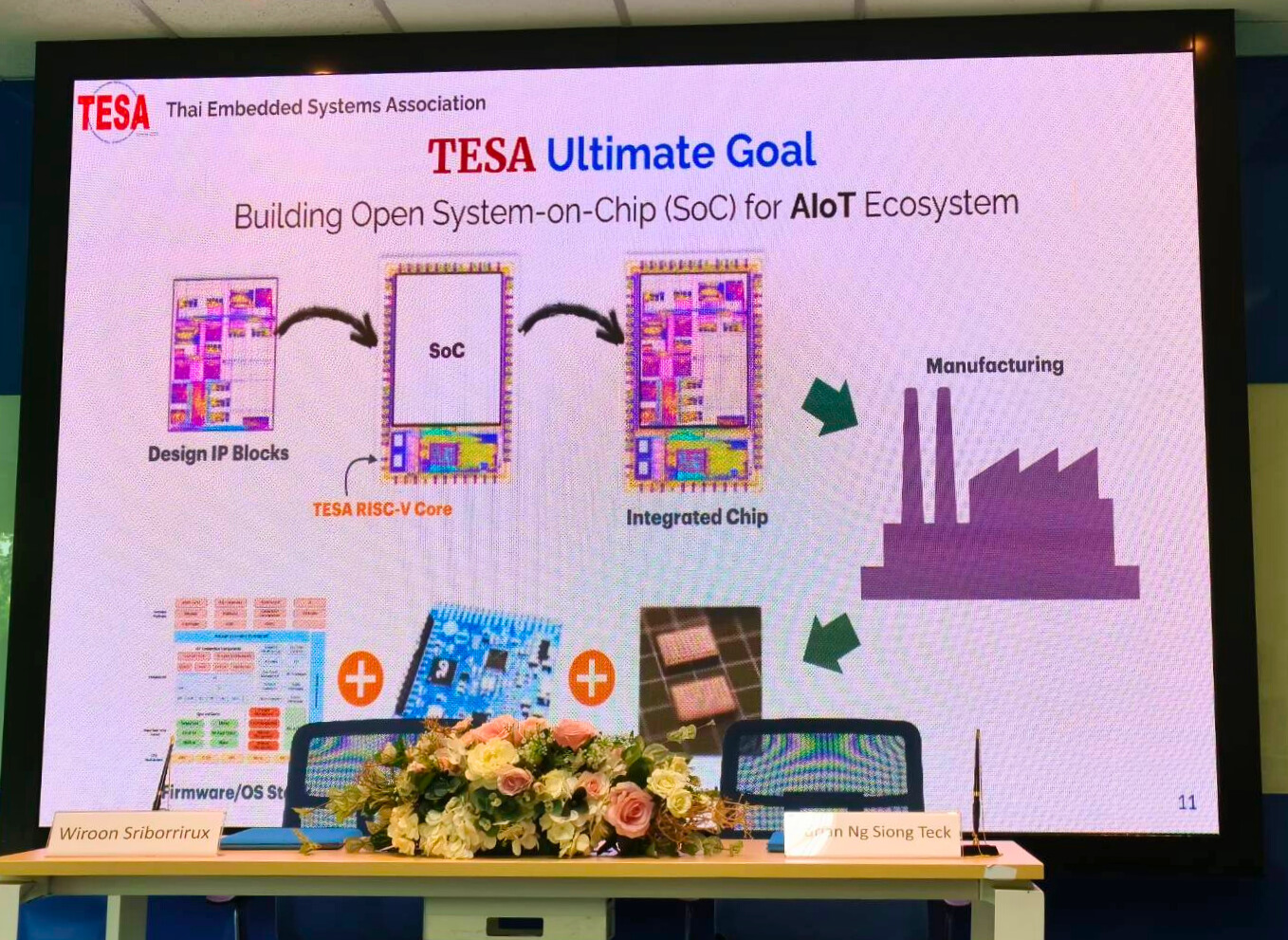

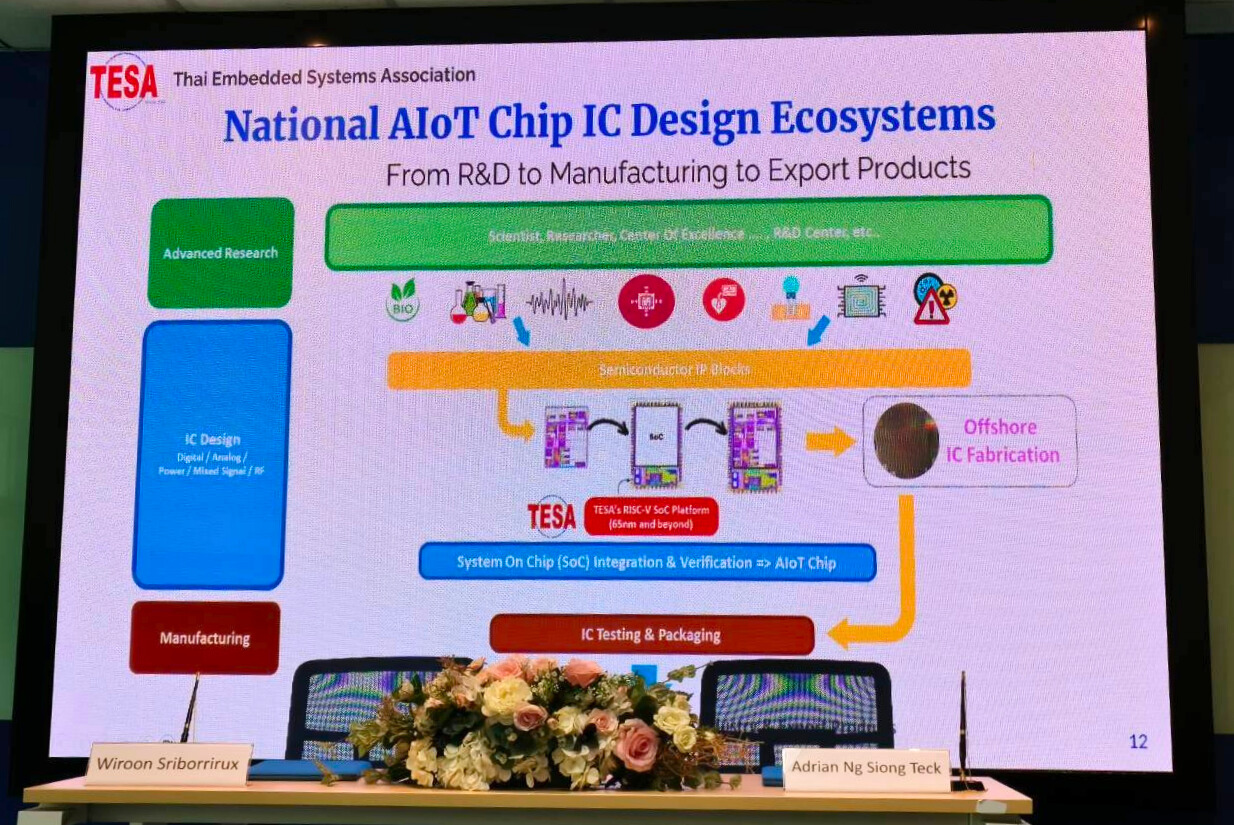

สมาคมสมองกลฝังตัวไทย (TESA) ร่วมกับ Synopsys และเครือข่ายพันธมิตรภาคการศึกษาและภาคอุตสาหกรรม เปิดตัวโครงการ “Thai RISC-V SoC Design Professional Program for Advanced Industry Development” มุ่งยกระดับบุคลากรไทยด้านการออกแบบระบบบนชิป (System-on-Chip: SoC) โดยใช้สถาปัตยกรรม RISC-V เป็นแกนหลัก เพื่อมุ่งสู่การผลิตชิปจริงและเสริมศักยภาพการพึ่งพาเทคโนโลยีได้ด้วยตนเอง โครงการนี้เกิดจากความร่วมมือระหว่าง 7 สถาบันการศึกษา และ 4 บริษัทชั้นนำ โดยมี สถาบันเทคโนโลยีไทย-ญี่ปุ่น เป็นสถาบันการศึกษาเอกชนเพียงแห่งเดียว ที่ได้รับเลือกเป็นมหาวิทยาลัยนำร่อง ในส่วนของ TNI: Thai-Nichi นำโดย ดร.จิรายุ ปีตะกุล อาจารย์ประจำคณะวิศวกรรมศาสตร์ แกนนำด้านเทคนิคและผู้ออกแบบหน่วยประมวลผลทางปัญญาประดิษฐ์ (Neural Processing Unit: NPU) ที่จะบูรณาการร่วมกับ RISC-V SoC เพื่อเพิ่มศักยภาพการประมวลผลด้าน AI พร้อมต่อ ยอดสู่การใช้งานจริง การอบรมเน้นการพัฒนาบุคลากรระดับ Train the Trainer ครอบคลุมตั้งแต่พื้นฐานด้าน Digital Design, สถาปัตยกรรมคอมพิวเตอร์ และ RISC-V ไปจนถึงเทคนิคการออกแบบชิปขั้นสูง เช่น Low-power Design, Noise Management และ Mixed-signal Design โดยได้รับการสนับสนุนจาก Synopsys ทั้งด้านเครื่องมือออกแบบอิเล็กทรอนิกส์ (EDA Tools) หลักสูตรมาตรฐานสากล และคำปรึกษาทางเทคนิค พิธีลงนามความร่วมมือจัดขึ้นเมื่อวันที่ 8 สิงหาคม 2568 ณ สำนักงานนวัตกรรมแห่งชาติ (NIA) นับเป็นก้าวสำคัญของอุตสาหกรรมออกแบบชิปในประเทศไทย และยังเป็นรากฐานในการเปิดหลักสูตร วิศวกรรมเซมิคอนดักเตอร์ (SC) ของ TNI: Thai-Nichi ซึ่งมีแผนเปิดรับนักศึกษารุ่นแรกในปี 2569 เพื่อสร้างบุคลากรไทยให้พร้อมสำหรับอุตสาหกรรมชิปและ AI ในอนาคต

SHARE :